Moin wollt auch mal zeigen was ich grad so treib…

Angefangen hats mit dem Nachbau einer Halbbrücke zum Ferritkerne testen, den Schaltplan findet man zig mal durchs Netz gestreut, nur das Original mit dem griffigen Namen find ich nicht mehr wieder ![]() .

.

Ich wollte dann mehr + ein par dumme Fehler ausmerzen also wuchs der Halbbrücke ne Vollbrücke und das aktuelle Projektziel wurd noch undefinierter.

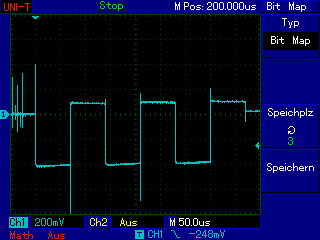

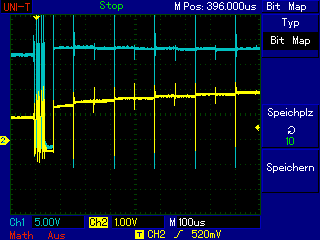

Aktuell erforsche ich damit für mich die PSFB Topologie, weil sind eh nur 2 IO mehr aber viel mehr Kontrolle möglich.

Die Schaltung selbst ist eher unspektakulär, IR2110 bootstrap gate drive, alles grob selbst durchgerechnet ABER das erste mal in meinem Leben das so eine Schaltung läuft und nicht nur stundenlang das Netzteil auf C.C. zieht bis ich frustriert aufgeb ![]()

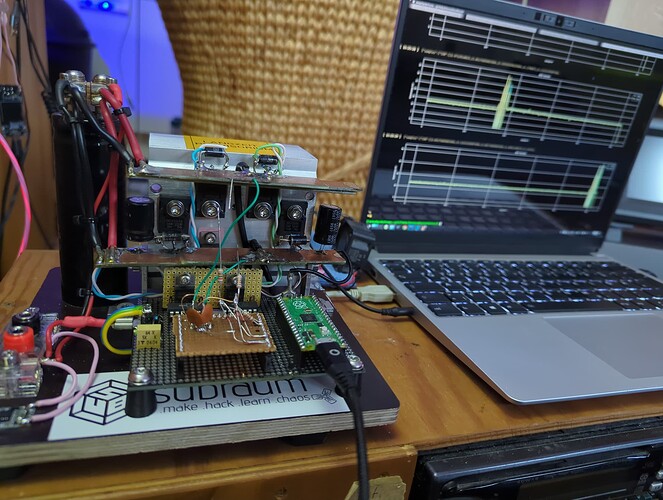

Hier mal ein Bild vom Aufbau, Schalten tun hier 4x IRFP064N, der Dummy-DUT aus 12x 12Ω parallel ist hinterm Kühlkörper:

Langfristig möchte ich auch gern mal nen eigenen Induktionserhitzer bauen, mikrocontrollerbasiert und eigensicher, so das er einfach nur schadfrei “nope” sagen kann wenn jemand statt der work coil nen fetten Anlaufkondi anklemmt.

Naja vllt. nicht ganz so extrem, aber vom Prinzip her halt…

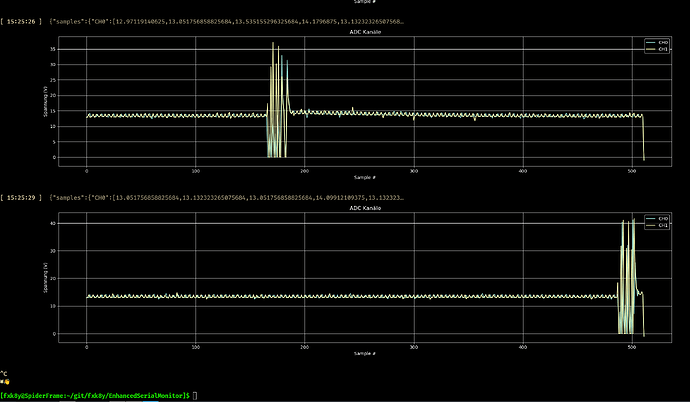

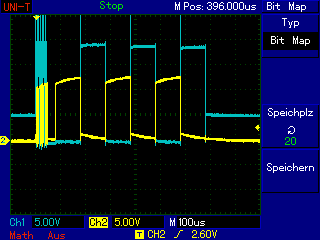

Als nächstes wird der interne ADC gegen nen TLC5510 getauscht, wie man hier sieht ist der nämlich deutlich zu lahm (RP2040, prescaler=0, 2 Kanäle round-robin):

(ja der DMA läuft noch asynchron zum Rest)

Wenn der neue ADC dran ist kann ich mich weiter der geplanten start-up Prozedur widmen, den DUT einmal sanft anschwingen und vermessen, Betriebsparameter schätzen und los gehts.

Versorgung sind zum Entwickeln ganz nett einfach 20V USB-PD, und auch wenn ich damit sicher keinen Blumentopf gewinn, technisch gesehen fällts irgendwie doch unter Leistungselektronik ![]()